トップ:http://galaxy.u-aizu.ac.jp/note/wiki/CAEX2022

主制御ユニット作成時の注意点

主制御ユニットの動作記述(behavioral)作成時に、一番最初の"module"で始まる行はコピーしないこと。この部分がsymbolの定義と異なると、回路のシミュレーションをする時(elaboration時)に、異なるポートが接続されてエラーとなります。

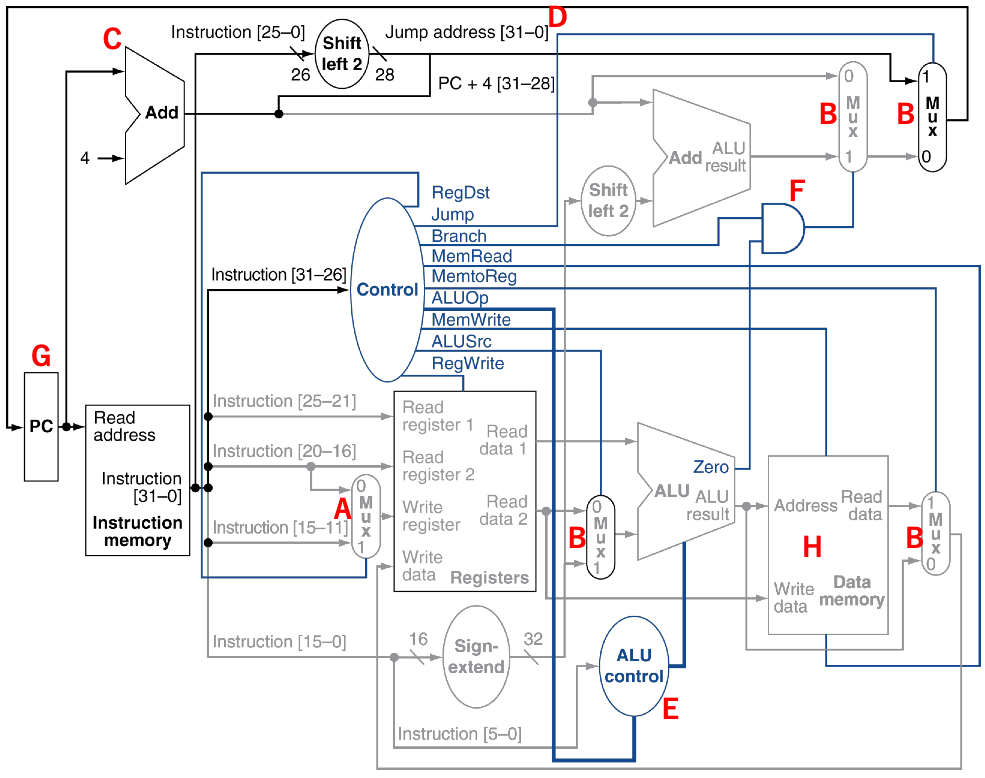

配線図

留意点1

マルチプレクサの入力(0と1)に注意して正しくつなぐこと。また、図Aは5 bitのマルチプレクサであり、図Bは32 bitのマルチプレクサである。

留意点2

図Cは32 bit 加算器であり、プログラムカウンタ(PC) + 4を計算する。これにはu_aizuライブラリの"Add"を使うこと

留意点3

図Dの信号(Jump address)は、図Cの加算器出力の上位4ビットと、命令の下位26ビットを左に2シフトしたものをつなげたアドレスとなる。

留意点4

主制御ユニットの真理値表は教科書上巻260ページの図4.22にある。Jump命令は261ページを参考にする。immediate命令についてはR-形式命令との違いを考慮して考えること。

留意点5

ALU制御ユニット(図E)のOpcode<5:0>には命令の上位6ビット(こちらは配線図では省略されていること注意)、Funct<5:0>には命令の下位6ビットを接続する こと。

留意点6

図Fは論理和であり、xc4000の"And2"を使うこと。

留意点7

図GはPCの32 bit レジスタ。レジスタの"ce"は"one"(xvcc)を接続すること。

留意点8

図Hの"Data memory"の入力ポート"CLK"には"CK"(クロック)を接続する。 シミュレーション時に、Data memoryの出力は、アドレス(ALUの出力)によっては不定(波形が赤くなる)場合があり、それは無視しても構わない。

留意点9

シミュレーションの結果はrun directoryの下の"simout.tmp"にログファイルがあるので、それを参照すること。

Attachments (1)

- MIPS_hint.png (158.1 KB) - added by nakasato 4 years ago.

Download all attachments as: .zip