| Version 4 (modified by nakasato, 11 years ago) (diff) |

|---|

トップ:http://galaxy.u-aizu.ac.jp/note/wiki/CAEX2015

概要

用意されたパイプラインプロセッサを使用して、フォワーディング・ストールの動作を理解すること。

準備

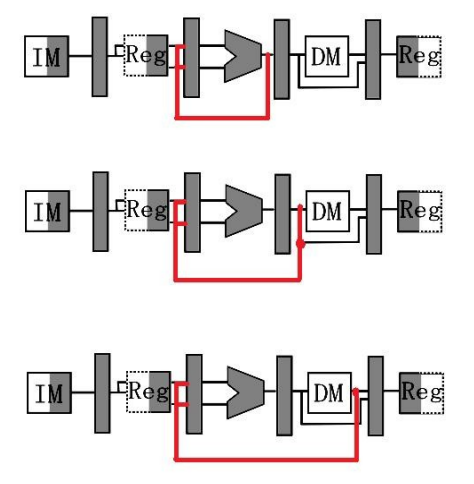

この演習では、事前に設計してあるパイプラインプロセッサを用いる。 このパイプラインプロセッサでは、演習で設計したマルチサイクルのプロセッサをベースに、 パイプライン化を行い、ID ステージで正しく分岐ができるようにフォワーディング回路を追加してある。 教科書と違い、フォワーディングをEX ステージ、MEM ステージ、データメモリからIDステージへ向けて行うことに注意すること。 このような差異は実装するデバイスや設計思想の違いによって起こる。

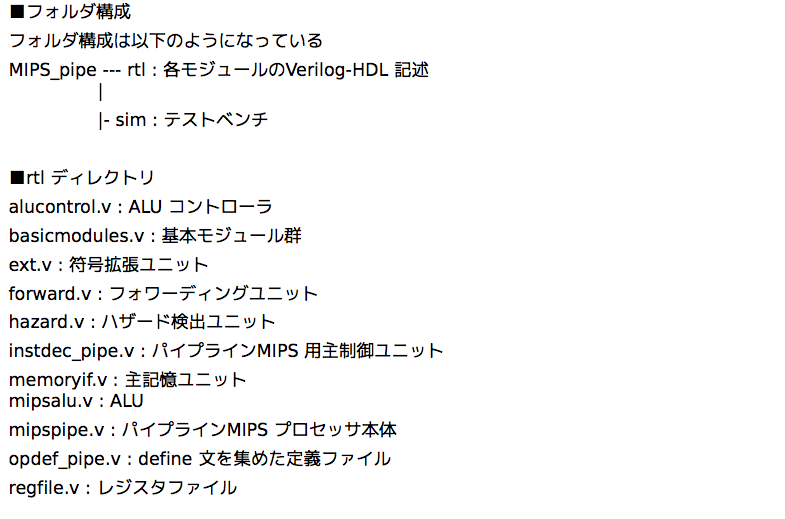

以下のファイルをダウンロードしたうえで、各自のディレクトリに展開すること。

http://galaxy.u-aizu.ac.jp/note/raw-attachment/wiki/Ex12%E8%AA%B2%E9%A1%8C2015/MIPS_pipe.tgz

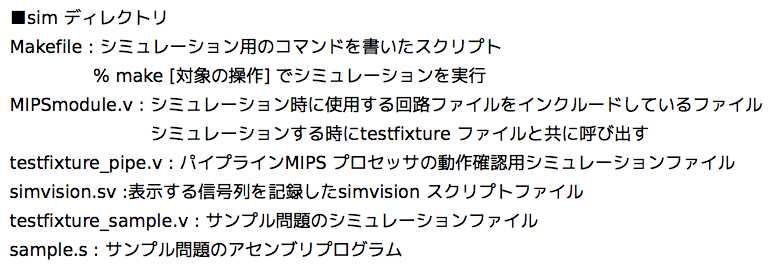

シミュレーションをおこなうには、Linux機にログインしてから、 「MIPS_pipe/sim」ディレクトリに移動し、「make sim」でncverilogによるコンパイルと実行がされる。 さらに自動的にsimvisionが起動されるので、以下の実行波形を確認すること。

上記図中のA の信号線(id_stall)がアサートされているサイクルは、ストールが発生していることを示し ている。このときはIF ステージのPC の値が進まないことを確認せよ。

また図中B の信号(fwd_から始まる信号)がアサートされているサイクルでは、 対応するフォワーディングパスからデータが転送されていることを示している。

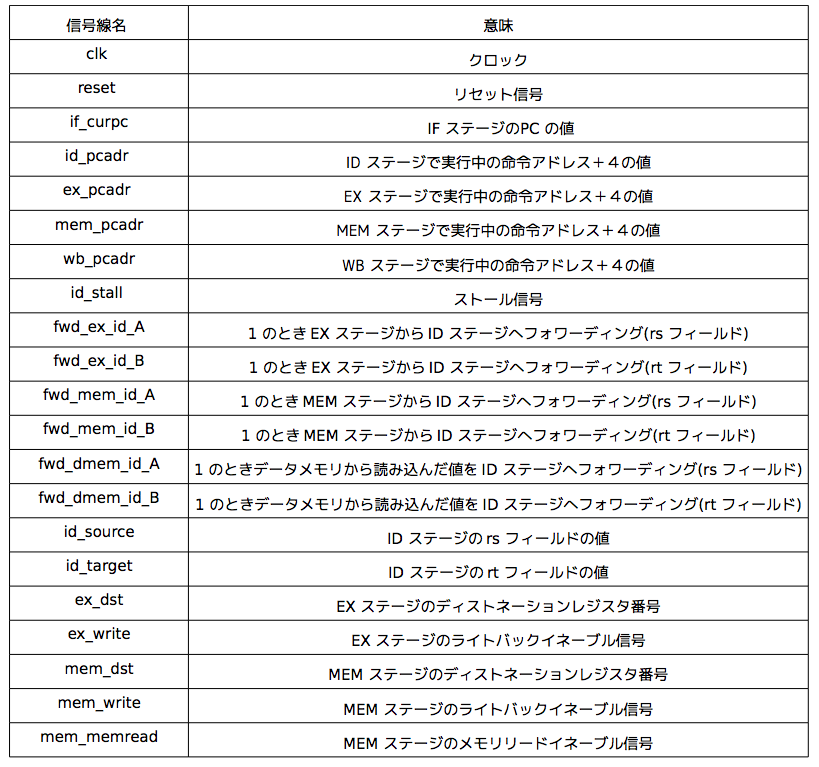

各信号線の意味

課題1 アセンブリプログラムのシミュレーション

準備

シミュレーションするプログラムごとに「sim」ディレクトリをコピーすること

cd MIPS_pipe cp -r sim problem1

任意のプログラムのシミュレーションをおこなうには、「testfixture_sample.v」を編集して、メモリの初期化をする必要がある。

以下の2つのプログラムについて、シミュレーションを行った後に波形を確認し、 なぜフォワーディング及びストールが起こっているかを考察せよ。 具体的に、どの命令でフォワーディングが起こっているか、またその理由は何かを答えなさい。

これらのプログラムでは複数のnop 命令(プログラム中のor/ori)でテストする命令列を挟み込み、 回答に関係のない依存が起こらないように記述してあることに注意すること。 また、プログラムの変数の値を適宜変更し、意図通りに動作していることを確認せよ。

解析を行う際には、命令と命令が格納されているアドレスおよびPC の値を注意深く追いかけること。 特にパイプライン動作ではIF, ID, EX, MEM, WB ステージで動作している命令が異なるため、 パイプラインの動作状況をよく確かめること。

プログラム1

.data

A: .word 3

B: .word 4

C: .word 5

D: .word 6

E: .word 0

F: .word 0

G: .word 0

.text

main: lw $t3, A

lw $t4, B

lw $t5, C

lw $t6, D

ori $s0, $0, 0

ori $s1, $0, 0

ori $s2, $0, 0

ori $s3, $0, 0

ori $s4, $0, 0

add $t2, $t3, $t4

add $t4, $t5, $t6

add $t5, $t3, $t4

ori $s5, $0, 0

ori $s6, $0, 0

ori $s7, $0, 0

sw $t2, E

sw $t4, F

sw $t5, G

exit: j exit

プログラム2

.data

A: .word 4

B: .word 20480

C: .word 16

D: .word 32

S: .word 0

.text

main: lw $t2, A

lw $t4, B

lw $t6, C

or $t1, $0, $0

or $t1, $0, $0

or $t1, $0, $0

or $t1, $0, $0

or $t1, $0, $0

add $t3, $t4, $t6

sub $t5, $t3, $t2

lw $t7, 0($t5)

add $t8, $t7, $t2

or $t1, $0, $0

or $t1, $0, $0

sw $t8, S

exit: j exit

課題2 プログラムの高速化

パイプラインプロセッサを高速に動作させるためには、 実行する命令間の依存関係を考慮し、アセンブリプログラムを設計する必要がある。 Ex03の例題4(バプルソート) を題材に、パイプラインストールが発生している部分に着目し、 これを改変する事によってなるべく高速に動作するプログラムを作成しなさい。

Attachments (1)

- MIPS_pipe.tgz (180.3 KB) - added by nakasato 11 years ago.

Download all attachments as: .zip