| Version 11 (modified by nakasato, 10 years ago) (diff) |

|---|

トップ:http://galaxy.u-aizu.ac.jp/note/wiki/CAEX2016

以下作成中

マルチサイクルプロセッサの制御

マルチサイクルプロセッサでは、ひとつの命令を複数のステップ(サイクル)に渡って実現します。 その各ステップで利用する信号、モジュールが異なります。その動作をまとめたものが以下の状態遷移図です。

状態遷移図:http://galaxy.u-aizu.ac.jp/note/raw-attachment/wiki/Ex08%E8%AA%B2%E9%A1%8C2016/FSM.pdf

この状態遷移図では状態は0から12の13状態が定義されています。 各状態には、その時に出力されるべき信号名とその値が書いてあります。

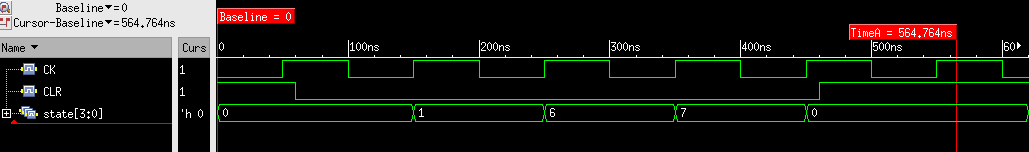

例えばR形式命令の場合、1サイクルごとに「0→1→6→7」と遷移することがわかります。 他の命令の場合も「0→1」の遷移は共通です。状態0は命令フェッチ、状態1は命令デコード&レジスタ読み出しをおこないます。

状態0では、以下の動作が同時に実施されます。

- メモリから現在のPCのアドレスにある命令を読み出す。

- PC+4を計算してPCを更新する。

そのためメモリのアドレスにはPCの値を入力すると同時にメモリを読み込むための信号(MemRead)を真に(アサート)します。 またメモリから読み出す値が命令かデータかを判別する信号IoDは、偽に(ネゲート)します。 さらに、IRWriteをアサートすることで、読み出された命令がメモリレジスタ(MDR)に保持されます。

ALUの入力AにはPCの値を入力するため、それを制御する信号ALUSrcAはネゲートします。 ALUの入力Bには"4"を入力するので、それを制御する信号ALUSrcB(2 bit)は"01"となり、 ALUは加算をするため、それを制御する信号ALUOp(2 bit)は"00"とします。 その結果をPCレジスタに書き込むため、PCWriteはアサートされ、PCSource(2 bit)は"00"となります。

状態1では、以下の動作が同時に実施されます。

- 次のサイクルで計算に利用するレジスタの値を読み出す

- ジャンプ先のアドレスを計算する

制御部の設計(1)

制御部モジュールのテンプレートは以下のようになります。

module ControlUnit(PCWriteCond, PCWrite, IorD, MemRead, MemWrite, MemtoReg,

IRWrite, PCSource, ALUOp, ALUSrcB, ALUSrcA,

RegWrite, RegDST, Op, CK, CLR);

// clock

input CK;

input CLR;

// opcode (6 bit)

input [5:0] Op;

// 1 bit control signal

output PCWriteCond;

output PCWrite;

output IorD;

output MemRead;

output MemWrite;

output MemtoReg;

output IRWrite;

output RegWrite;

output RegDST;

output ALUSrcA;

// 2 bit control signal

output [1:0] PCSource;

output [1:0] ALUOp;

output [2:0] ALUSrcB;

// register declaration

reg PCWriteCond;

reg PCWrite;

reg IorD;

reg MemRead;

reg MemWrite;

reg MemtoReg;

reg IRWrite;

reg [1:0] PCSource;

reg [1:0] ALUOp;

reg [2:0] ALUSrcB;

reg ALUSrcA;

reg RegWrite;

reg RegDST;

// state register

reg [3:0] state;

endmodule // ControlUnit

入力信号はOpとCK(クロック信号)とCLR(リセット信号)で、その他は出力になります。 Op信号はMIPS命令コードの25-31ビットの部分です。各命令コードごとのOp信号を以下のテーブルに示します。

命令コード

| 命令の種類 | opcode(10進数) |

| R形式 | 0 |

| Load Word | 35 |

| Store Word | 43 |

| Branch on EQ | 4 |

| ADD imm | 8 |

| SLT imm | 10 |

| AND imm | 12 |

| ORI imm | 13 |

注意:R形式命令では、命令コードの0-5ビットの部分で演算の種類を指定します。

例題

状態遷移図から、R形式命令の実行には4サイクル必要になります。 このことを、以下のファイルを使ってシミュレーションを行い確かめなさい。

状態遷移のみの制御回路

テストベンチファイル

実行例

それぞれのファイルをダウンロードまたは保存して、以下のコマンドを実行。

ncverilog CUbench_1.v

この状態遷移の回路では、always文の部分はCLKが上向きに変化する時に状態が遷移します。 また、CLR信号が真になったら状態0になります(リセット)。 そのため状態遷移を行う時にはCLR信号を適切に変化させる必要があります。

実行波形

課題

LW命令とADDI命令の場合に、例題を参考にテストベンチファイルを作成して、 シミュレーションを行い、実行波形を確認してください。 それぞれの場合、実行までに何サイクル必要かを考えること。

Attachments (5)

- FSM.pdf (43.8 KB) - added by nakasato 10 years ago.

- ControlUnit_1.v (2.0 KB) - added by nakasato 10 years ago.

- CUbench_1.v (1.0 KB) - added by nakasato 10 years ago.

- ControlUnit_2.v (2.6 KB) - added by nakasato 10 years ago.

- CUbench_2.v (6.6 KB) - added by nakasato 10 years ago.

Download all attachments as: .zip