| Version 2 (modified by nakasato, 10 years ago) (diff) |

|---|

トップ:http://galaxy.u-aizu.ac.jp/note/wiki/CAEX2016

マルチサイクルプロセッサの設計

これまでの演習で設計してきたモジュールを組み合わせて、MIPS ISA互換のマルチサイクルプロセッサを設計します。

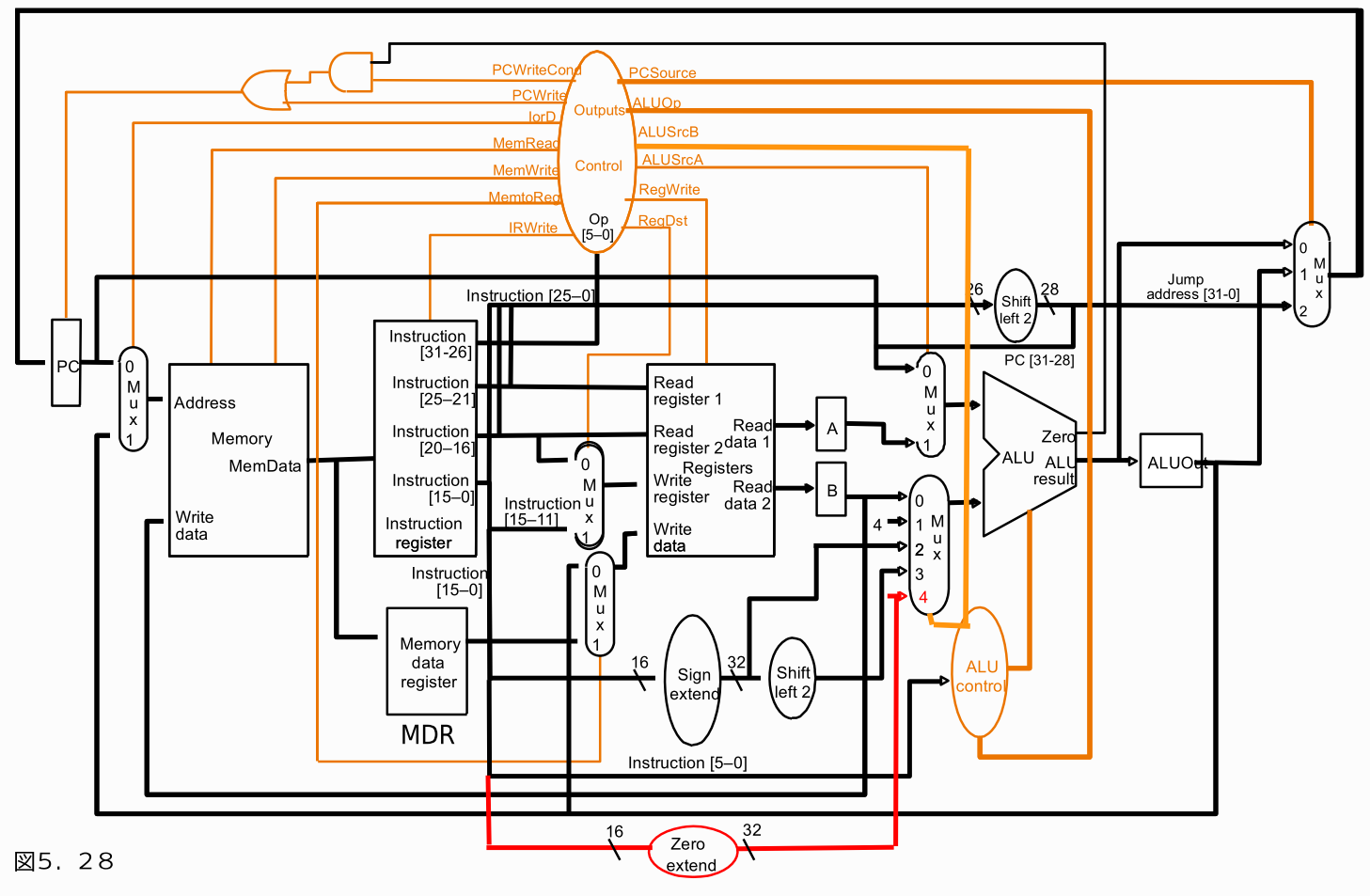

設計するプロセッサのブロック図全体図は以下のようになります。

ブロック図

詳細を見るためのPDF version -> http://galaxy.u-aizu.ac.jp/note/raw-attachment/wiki/Ex07%E8%AA%B2%E9%A1%8C2015/dp_ctl.pdf

設計の指針

- ブロック図を参照して、どのようなモジュールが必要かをリストアップする。

- それぞれのモジュールを設計する。

- モジュール間接続について考える。この時にモジュールごとに入力と出力の種類やbit幅を考慮する。

- "Datapath.v"を作成し、そこからモジュールのインスタンス化および接続をおこなう。

モジュールのリストアップ

プロセッサを完成させるには、ブロック図を参照して、必要なモジュールをリストアップします。 これまでの演習で利用してきた、あるいは設計してきたモジュールは:

- ALU (演習第4週)

- ALU control (演習第5週)

- Memory(メモリ)/Registers(レジスタファイル) (演習第6週)

です。その他に必要なモジュールを列挙すると以下になります。

- PCレジスタ

- Aレジスタ

- Bレジスタ

- ALUOutレジスタ

- Instruction register

- Memory data register

- 2 to 1 マルチプレクサ x 4

- 3 to 1 マルチプレクサ x 1

- 5 to 1 マルチプレクサ x 1

- Sign extendモジュール

- Zero extendモジュール

- "Shift left 2"モジュール x 2

- 制御部

各モジュールの設計

レジスタ

レジスタは全て32bitです。例えばAレジスタのHDL記述は以下のようになります。

module RegA(i, CK, CLR, o);

input CK, CLR;

input [31:0] i;

output [31:0] o;

reg [31:0] o;

always @(posedge CK) begin

if (CLR == 1'b1)

o <= 32'h00000000;

else

o <= i;

end

endmodule

CLRが真の時にレジスタは0x0にクリアされます。

レジスタのうちPCレジスタ、Instruction registerは、制御信号で書き込みが制御されます。

例えば、PCレジスタはPCloadが真の時のみにレジスタの内容をアップデートします。記述例は以下のようになります。

module RegPC(i, PCload, CK, CLR, o);

input CK, CLR, PCload;

input [31:0] i;

output [31:0] o;

reg [31:0] o;

always @(posedge CK) begin

if (CLR == 1'b1)

o <= 32'h00000000;

else if (PCload == 1'b1)

o <= i;

end

endmodule

Instruction register

ブロック図を見るとわかるように、このレジスタはメモリモジュールから出力を保持する32bitレジスタですが、 出力は4種の信号線に分かれます。このレジスタが命令を保持するレジスタであるからです。

例えば今実行中の命令がR形式命令の場合、21-25ビットの部分はレジスタのアドレスを表すので、 その信号はレジスタファイルの読み出しアドレス(Read register 1)に接続されています。 同様に、26-31ビットの部分は制御部のOpに接続されます。

よって、この命令レジスタは以下の入出力となるように設計してください。

module RegInst(i, IRWrite, CK, CLR, o0_15, o16_20, o21_25, o26_31); input CK, CLR, IRWrite; input [31:0] i; output [15:0] o0_15; output [4:0] o16_20, o21_25; output [5:0] o26_31; endmodule

マルチプレクサ

マルチプレクサは、制御信号に応じて、複数の入力から出力を選択します。

例えば、2入力から信号sに応じて、片方を選択する2 to 1マルチプレクサの記述は以下になります。

// 32bit : 2 to 1 multiplexer

module mux2(i0, i1, s, o);

input [31:0] i0, i1;

input s;

output [31:0] o;

reg [31:0] o; // always分で代入する場合にはreg宣言も必要

always @(i0 or i1 or s) begin

if (s == 1'b1)

o <= i1;

else

o <= i0;

end

endmodule

3入力以上のマルチプレクサはcase文で記述します。参考書の67ページを参照すること。 センシティビティリスト(「@()」の部分)に全ての入力信号を列挙する必要があることに注意すること。

Sign extendモジュール

このモジュールは入力が16bitで出力が32bitになります。

Zero extendモジュール

このモジュールも、入力が16bitで出力が32bitになります。

"Shift left 2"モジュール

このモジュールは2回利用されていて、どちらも入力を左に2 bitシフトしたものが出力です。

ただし、Sign extendモジュールに接続されているものは入出力とも32bitですが、 命令の0-25ビットが入力されているものは、入力が26bitで出力が28bitです。 この28bitの出力信号は、PCレジスタの28-31ビットと合わせて32bit信号になり、 一番右にあるマルチプレクサの入力になります。

制御部

制御部は図の上部中心にあるオレンジ色の部分で、この部分については別途説明します。

課題1 データパスの理解

以下のPDFで示された黄色い箱の番号(1 - 8)のデータパスの信号幅を答えなさい。

http://galaxy.u-aizu.ac.jp/note/raw-attachment/wiki/Ex07%E8%AA%B2%E9%A1%8C2016/dp_bit_width.pdf

課題2 モジュールの設計

制御部を除いて、リストアップされた必要なモジュールを設計してください。 そのうち、5 to 1マルチプレクサ、Sign extend、Zero extend、Shift left 2の各モジュールは、 テストベンチを書いて正しい動作をするかを確認してください。

Attachments (2)

- dp_bit_width.pdf (258.4 KB) - added by nakasato 10 years ago.

- dp_ctl.pdf (41.1 KB) - added by nakasato 10 years ago.

Download all attachments as: .zip