| Version 1 (modified by nakasato, 11 years ago) (diff) |

|---|

トップ:http://galaxy.u-aizu.ac.jp/note/wiki/CAEX2015

ALUの制御

第4版上巻p.291の「ALU制御ユニット」の項を参考にして、ALUを制御するためのユニットを設計します。

まずここで設計するALU制御ユニットのテンプレートは以下のようになります。

module ALUcontrol(ALUop,FA, FB, ALUoperation );

input [1:0] ALUop;

input [5:0] FA;// {F5,F4,F3,F2,F1,F0}

input [5:0] FB;// {F31,F30,F29,F28,F27,F26}

output [3:0] ALUoperation;

wire ALUOperation0, ALUOperation1, ALUOperation2;

assign ALUoperation0 = ...;

assign ALUoperation1 = ...;

assign ALUoperation2 = ...;

assign ALUoperation = {...};

endmodule

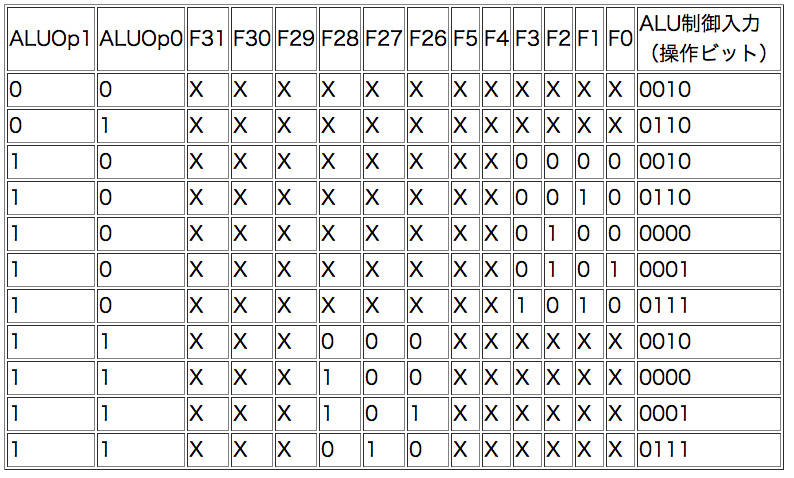

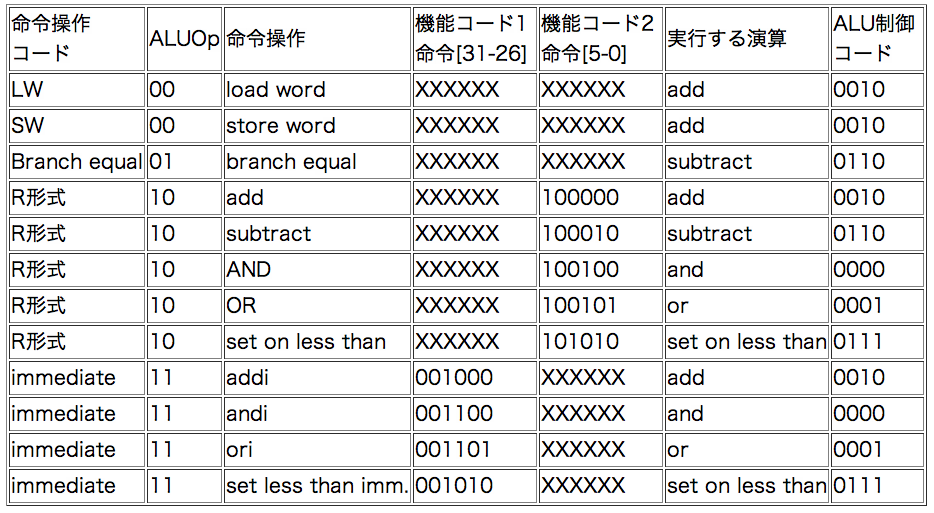

ALUop(2 bit)は主制御ユニットからの入力です。FAとFB(それぞれ6 bit)も入力です。 これはMIPS命令(32 bit)の一部を表します。 命令の各ビットを下位からF0-F31とした時に、FAはF0 - F5を、FBはF26 - F31を表すこととします。 ALU制御ユニットはALUop, FA, FBを組み合わせて、 教科書にあるようにALUを制御するための4 bitの信号を作る必要があります(図4.12と4.13)。 今回設計するプロセッサでは、イミディエート命令を追加するため、以下の修正が必要です。

追加されるイミディエート命令は、命令語の上位6ビット(FB)に演算の種類が入っているため、 イミディエート命令をサポートするためには、上位6ビットの内容もALU制御ユニットに入力しなければなりません。 さらに、何らかの手段によってALU制御ユニットに、現在実行中の命令がイミディエート命令であることを伝えなくてはなりません。

ここでは、ALUOpで未使用の組み合わせだった"2'b11"という値をイミディエート命令であることを表すことにします。

この結果、図4.12のALU制御ビットの構成は次のように変更されます。

上記の表に対応して、教科書図4.13、ALU制御コードの真理値表も以下のように拡張されます。

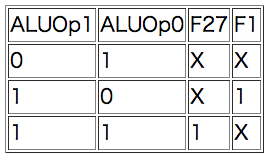

この真理値表をもとにして、出力であるALUoperation(4 bit)を設計してください。 まず、真理値表から、ALUoperation[3]は常に偽(0)であることがわかります。 他のビットは、それが真(1)になるになる条件を考えてください。 例えば、ALUoperation[2]が真になる組み合わせは:

の時です。

この真理値表の1行目だけを考慮すると、assign文を使って

assign ALUoperation[2] = (ALUop[1] == 1'b0 && ALUop[0] == 1'b1);

または

assign ALUoperation[2] = (ALUop == 2'b01);

と書くことができます。この文は括弧内の条件が満たされた時にALUoperation[2]が真となることを意味します。 真理値表の他の行もあわせて正しくなるように、ALUoperation[2]を定義してください。

ALUoperation[1]とALUoperation[0]は同様に真理値表を求めてから、assing文を考えてください。

課題:ALU制御ユニットを設計する

以上の説明に従ってALU制御ユニット(ファイル名"ALUControl.v")を設計しなさい。

設計するALU制御ユニットへの入力は"ALUop"と"FA"と"FB"であり、最初の図よりその組合せは11パターンあります (LWとSWは入力が同じのため)。 この11パターンの場合に正しい動作をするかどうかを、以下のテストベンチの例を参考にして動作検証をしなさい。

テストベンチのテンプレート:

`timescale 1ns/1ps

`include "ALUcontrol.v"

module ALUcontroltestbench;

reg [1:0] ALUop;

reg [5:0] FA;

reg [5:0] FB;

wire [3:0] ALUoperation;

ALUcontrol aluc(ALUop, FA, FB, ALUoperation);

initial

begin

$dumpfile("ALUcontroltestbench.vcd");

$dumpvars(0, aluc);

#0 ALUop = 2'b00; FA= 6'b000000; FB= 6'b000000; // LW&SW

#100

$display( $time, " ALUoperation=%h", ALUoperation); // should be "0010"

ALUop = 2'b01; FA= 6'b000000; FB= 6'b000000; // Branch on Equal

#100

$display( $time, " ALUoperation=%h", ALUoperation); // should be "0110"

// 以下残りの9パターンについて繰り返し

$finish;

end

endmodule

Attachments (3)

- ALU1.png (69.9 KB) - added by nakasato 11 years ago.

- ALU2.png (30.0 KB) - added by nakasato 11 years ago.

- ALU3.png (4.8 KB) - added by nakasato 11 years ago.

Download all attachments as: .zip